* Power: Turn off additional peripheral clock branches. * Update schematic with new symbol table and KiCad standard symbols. Fix up wires. * Schematic: Update power net labels. * Schematic: Update footprint names to match library changes. * Schematic: Update header vendor and part numbers. * Schematic: Specify (arbitrary) value for PDN# net. * Schematic: Remove fourth fiducial. Not standard practice, and was taking up valuable board space. * Schematic: Add reference oscillator -- options for clipped sine or HCMOS output. * Schematic: Update copyright year. * Schematic: Remove CLKOUT to CPLD. It was a half-baked idea. * Schematic: Add (experimental) GPS circuit. Add note about charging circuit. Update date and revision to match PCB. * PCB: Update from schematic change: now revision 20180819. Diff was extensive due to net renumbering... * PCB: Fix GPS courtyard to accommodate crazy solder paste recommendation in integration manual. PCB: Address DRC clearance violation between via and oscillator pad. * PCB: Update copyright on drawing. * Update schematic and PCB date and revision. * gitignore: Sublime Text editor project/workspace files * Power: Power up or power down peripheral clock at appropriate times, so firmware doesn't freeze... * Clocking: Fix incorrect shift for CGU IDIVx_CTRL.PD field. * LPC43xx: Add CGU IDIVx struct/union type. * Power: Switch off unused IDIV dividers. Make note of active IDIVs and their use. * HackRF Mode: Upgrade firmware to 2018.01.1 (API 1.02) * MAX V CPLD: Refactor class to look more like Xilinx CoolRunner II CPLD class. * MAX V CPLD: Add BYPASS, SAMPLE support. Rename enter_isp -> enable, exit_isp -> disable. Use SAMPLE at start of flash process, which somehow addresses the problem where CFM wouldn't load into SRAM (and become the active bitstream) after flashing. * MAX V CPLD: Reverse verify data checking logic to make it a little faster. * CPLD: After reprogramming flash, immediately clamp I/O signals, load to SRAM, and "execute" the new bitstream. * Si5351: Refactor code, make one of the registers more type-safe. Clock Manager: Track selected reference clock source for later use in user interface. * Clock Manager: Add note about PPM only affecting Si5351C PLLA, which always runs from the HackRF 25MHz crystal. It is assumed an external clock does not need adjustment, though I am open to being convinced otherwise... * PPM UI: Show "EXT" when showing PPM adjustment and reference clock is external. * CPLD: Add pins and logic for new PortaPack hardware feature(s). * CPLD: Bitstream to support new hardware features. * Clock Generator: Add a couple more setter methods for ClockControl registers. * Clock Manager: Use shared MCU CLKIN clock control configuration constant. * Clock Manager: Reduce MCU CLKIN driver current. 2mA should be plenty. * Clock Manager: Remove redundant clock generator output enable. * Bootstrap: Remove unnecessary ldscript hack to locate SPIFI mode change code in RAM. * Bootstrap: Get CPU operating at max frequency as soon as possible. Update SPIFI speed comment. Make some more LPC43xx types into unions with uint32_t. * Bootstrap: Explicitly configure IDIVB for SPIFI, despite LPC43xx bootloader setting it. * Clock Manager: Init peripherals before CPLD reconfig. Do the clock generator setup after, so we can check presence of PortaPack reference clock with the help of the latest CPLD bitstream. * Clock Manager: Reverse sense of conditional that determines crystal or non-crystal reference source. This is for an expected upcoming change where multiple external options can be differentiated. * Bootstrap: Consolidate clock configuration, update SPIFI rate comment. * Clock Manager: Use IDIVA for clock source for all peripherals, instead of PLL1. Should make switching easier going forward. Don't use IRC as clock during initial clock manager configuration. Until we switch to GP_CLKIN, we should go flat out... * ChibiOS M0: Change default clock speed to 204MHz, since bootstrap now maxes out clock speed before starting M0 execution. * PortaPack IO: Expose method to set reference oscillator enable pin. * Pin configuration: Do SPIFI pin config with other pins, in preparation for eliminating separate bootloader. * Pin configuration: Disable input buffers on pins that are never read. * Revert "ChibiOS M0: Change default clock speed to 204MHz, since bootstrap now maxes out clock speed before starting M0 execution." This reverts commit c0e2bb6cc4cc656769323bdbb8ee5a16d2d5bb03. * Remove unused board files. * Add LPC43xx functions. * chibios: Replace code with per-peripheral structs defining clocks, interrupts, and reset bits. * LPC43xx: Add MCPWM peripheral struct. * clock generator: Use recommended PLL reset register value. Datasheet recommends a value. AN619 is quiet on the topic, claims the low nibble is default 0b0000. * GPIO: Tweak masking of SCU function. I don't remember why I thought this was necessary... * HAL: Explicitly turn on timer peripheral clocks used as systicks, during init. * SCU: Add struct to hold pin configuration. * PAL: Add functions to address The Glitch. https://greatscottgadgets.com/2018/02-28-we-fixed-the-glitch/ * PAL/board: New IO initialization code Declare initial state for SCU pin config, GPIOs. Apply initial state during PAL init. Perform VAA slow turn-on to address The Glitch. * Merge M0 and M4 to eliminate need for bootstrap firmware During _early_init, detect if we're running on the M4 or M0. If M4: do M4-specific core initialization, reset peripherals, speed up SPIFI clock, start M0, go to sleep. If M0: do all the other things. * Pins: Miscellaneous SCU configuration tweaks. * Little code clarity improvement. * bootstrap: Remove, not necessary. * Clock Manager: Large re-working to support external references. * Fix merge conflicts

HAVOC is a fork of the PortaPack H1 firmware, a portability add-on for the HackRF One software-defined radio.

Hardware is available at ShareBrained Technology.

It is build on top of ShareBrained's firmware, meaning that the original functionalities are kept (except when I don't sync for 2 months).

Documentation

If you want to submit a bug report, suggest something... Don't hesitate, use this page: https://github.com/furrtek/portapack-havoc/issues (Check the progress list below first).

Summary

As its name implies, HAVOC's functionalities can be fun, mean and even useful sometimes. You shouldn't use them. No ! Bad ! Put it down.

In most countries, radio transmissions are tightly regulated. Transmitting outside of free/public bands without a licence or authorization, even at very low power, is certainly forbidden where you live. Always bear that in mind. You're the ONLY ONE responsible for what you do with this software.

Fork features

- IQ file replay

- Microphone FM transmit with CTCSS

- CTCSS decoder

- Frequency manager (save & load from SD card, with categories and notes)

- File manager

- "Soundboard" wave file player (put 8-bit mono files in SD card /wav directory)

- ADS-B receiver with map view

- ADS-B transmitter (aircraft spoof)

- SSTV transmitter

- Fully configurable jammer

- POCSAG transmitter

- POCSAG receiver/decoder

- Morse transmitter (FM tone and CW)

- OOK transmitter for common remote encoders (PT2262, doorbells, remote outlets, some garage doors, ...)

- RDS (Radio Data System) PSN, RadioText and Time groups transmitter

- Meteorological radiosonde receiver for M10 and M2K2...

- AFSK receiver

- AFSK transmitter (Bell202...)

- Nuoptix DTMF sync transmitter (quite specific but can be useful in some theme parks :) )

- TouchTunes jukebox universal remote (by Notpike)

- LCR (Language de Commande Routier) message generator

- Street lighting control transmitter (CCIR tones)

- "Play Dead" in case of emergency

- Fully configurable RF signal generator

- RSSI audio output as pitch (for direction finding)

Progress

| Feature | Progress | Notes |

|---|---|---|

| POCSAG RX | 95% | Needs support for numeric messages |

| Morse TX | 95% | Needs fox hunt scheduler and live keying mode |

| Mic. TX | 95% | Carrier leak bug, need to find guard tones for various brands of wireless mics |

| ADS-B RX | 90% | Needs angle and speed decoding |

| Close-Call™ | 85% | Needs adjustments and optimization for wider frequency range |

| ADS-B TX | 85% | Works but baseband module needs cleaning |

| SSTV TX | 80% | Needs better bitmap file handling, support for other modes (ROBOT ?) and callsign FSK ID |

| Radiosondes | 75% | Needs support for other models |

| Wave visualizer | 70% | Needs cleaning and handling of other sample formats, high priority |

| AFSK RX | 70% | Needs work regarding flexibility |

| Sigfox RX | 40% | Tuning basics done, needs decoding code and testing |

| Generic TXs | 30% | Raw AX.25, AFSK, FSK, CCIR, DTMF... Tonesets are ready |

| CC1101 TRX | 10% | And other sub-GHz transceiver chips like SI4032... |

| SSTV RX | 0% | |

| Scanner | 0% | Easy, could be used with POCSAG RX to catch jumping channels |

| SSB TX | 0% | Requested but math is hard :( |

| OOK RX | 0% | See if rtl_433's author is fine with using protocol defs |

| Analog TV TX | 0% | Enough CPU ? B&W and no sound ? |

| LoJack RX | 0% | Basically AFSK RX |

| DMR info RX | 0% | Retrieve DMR channel info. No voice because of vocoder complexity and possible legal issue |

| Tetra info? | 0% | Same |

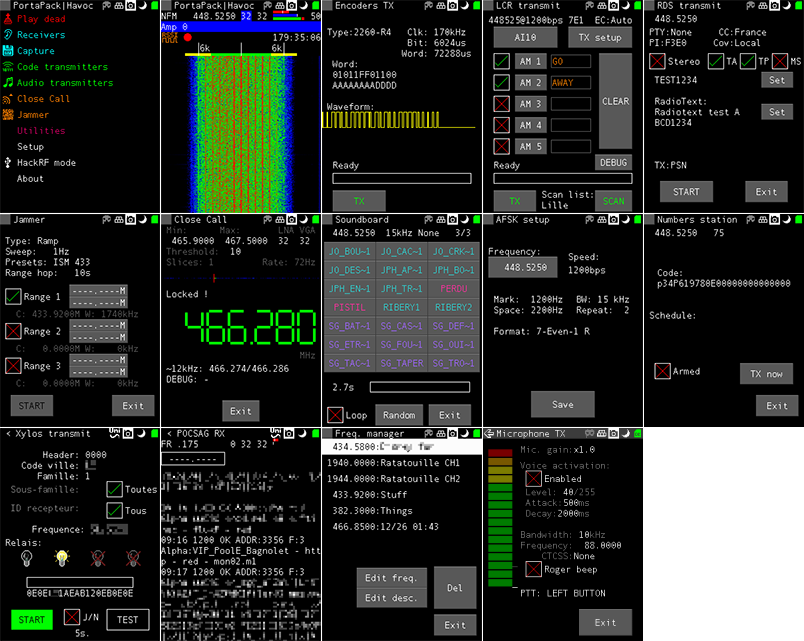

Screenshots

Thanks

- Sig and cLx for research on AFSK LCR, Xylos, and for lending remote-controlled outlets

- Pyr3x, Rainer Matla and DC1RDB for the donations :)

- Keld Norman and Giorgio Campiotti for ideas and suggestions

License

Except where specified in subdirectories of this project, all work is offered under the following license:

Copyright (C) 2013-2015 Jared Boone, ShareBrained Technology, Inc.

Copyright (C) 2015-2016 Furrtek

This program is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 2 of the License, or (at your option) any later version.

This program is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with this program; if not, write to the Free Software Foundation, Inc., 51 Franklin Street, Fifth Floor, Boston, MA 02110-1301, USA.

Contact

Original firmware and hardware

Jared Boone jared@sharebrained.com

ShareBrained Technology, Inc.

The latest version of this repository can be found at https://github.com/sharebrained/portapack-hackrf/

HAVOC specific things

Furrtek furrtek@gmail.com